SLUS564C – JULY 2003 – REVISED OCTOBER 2008

# DUAL, VOLTAGE MODE, DDR SELECTABLE, SYNCHRONOUS, STEP-DOWN CONTROLLER FOR NOTEBOOK SYSTEM POWER

#### FEATURES

- Wide Input Voltage Range: 4.5-V to 28-V

- Selectable Dual and DDR Modes

- Selectable Fixed Frequency Voltage Mode

- Advanced Power Good Logic Monitors both Channels

- Selectable Autoskip Mode

- Integrated Boot Strap Diodes

- 180° Phase Shift Between Channels

- Integrated 5-V, 60-mA Regulator

- Input Feedforward Control

- 1% Internal 0.85-V Reference

- R<sub>DS(on)</sub> Overcurrent Detection (4200 ppm/°C)

- Integrated OVP, UVP and Power Good Timers

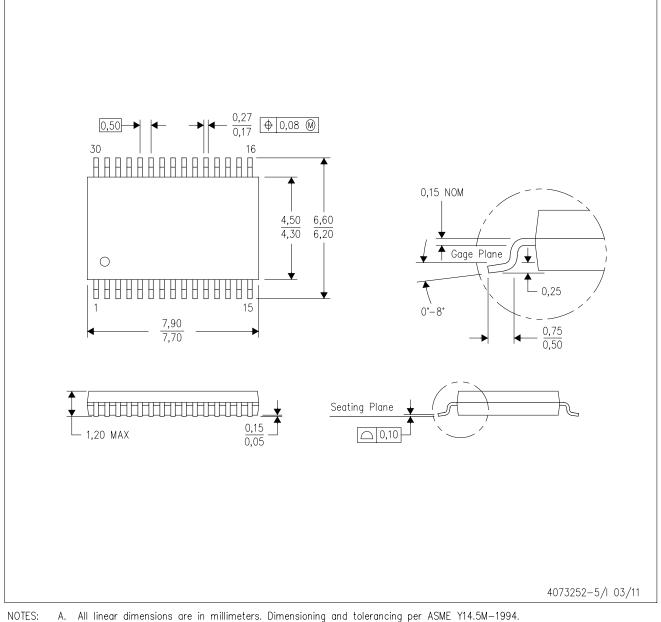

- 30-pin TSSOP Package

#### **APPLICATIONS**

- Notebook Computers System Bus and I/O

- DDR I or DDR II Termination

#### DESCRIPTION

The TPS51020 is a multi-function dualsynchronous step-down controller for notebook system power. The part is specifically designed for high performance, high efficiency applications where the loss associated with a current sense resistor is unacceptable. The TPS51020 utilizes feed forward voltage mode control to attain high efficiency without sacrificing line response. Efficiency at light load conditions can be maintained high as well by incorporating autoskip operation. A selectable, Suspend to RAM (STR) supported, DDR option provides a one chip solution for all switching applications from 5-V/3.3-V supply to a complete DDR termination solution.

### **ORDERING INFORMATION**

| ТА            | PLASTIC TSSOP (DBT) |  |  |  |

|---------------|---------------------|--|--|--|

| 4000 / 0500   | TPS51020DBT         |  |  |  |

| –40°C to 85°C | TPS51020DBTR (T&R)  |  |  |  |

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SLUS564C - JULY 2003 - REVISED OCTOBER 2008

#### **ABSOLUTE MAXIMUM RATINGS**

Over operating free-air temperature range unless otherwise noted. All voltage values are with respect to the network ground terminal unless otherwise noted. (1)

|                          |                                                                           | TPS51020    | UNIT |  |

|--------------------------|---------------------------------------------------------------------------|-------------|------|--|

|                          | VBST1, VBST2                                                              | -0.3 to 35  |      |  |

|                          | VBST1, VBST2 (with respect to LL)                                         | -0.3 to 7   |      |  |

| Input voltage range      | VIN, TRIP1, TRIP2, ENBL1, ENBL2, DDR                                      | -0.3 to 30  |      |  |

|                          | SKIP, INV1, INV2                                                          | -0.3 to 7   |      |  |

|                          | OUT1_U, OUT2_U                                                            | -1 to 35    |      |  |

|                          | OUT1_U, OUT2_U (with respect to LL)                                       | -0.3 to 7   | V    |  |

|                          | LL1, LL2                                                                  | -1 to 30    |      |  |

| Ouput voltage range      | REF_X                                                                     | -0.3 to 15  | 7    |  |

|                          | PGOOD, VO1_VDDQ, VO2, OUT1_D, OUT2_D, COMP1, COMP2, VREG5, SSTRT1, SSTRT2 | -0.3 to 7   |      |  |

|                          | OUTGND1, OUTGND2                                                          | -0.3 to 0.3 |      |  |

|                          | VREG5                                                                     | 70          |      |  |

| Output current range     | REF_X                                                                     | 7           | mA   |  |

| Operating free-air tempe | erature range, T <sub>A</sub>                                             | -40 to 85   |      |  |

| Storage temperature rai  | -55 to 150                                                                |             |      |  |

| Junction temperature ra  | -40 to 125                                                                | °C          |      |  |

| Lead temperature 1,6 m   | nm (1/16 inch) from case for 10 seconds                                   | 300         |      |  |

#### **RECOMMENDED OPERATING CONDITIONS**

|                                |                                     | м  | IN TYP | MAX | UNIT |

|--------------------------------|-------------------------------------|----|--------|-----|------|

| Supply voltage, VIN            |                                     |    | 5      | 28  |      |

| Supply voltage, VBST1, VBST2   |                                     |    |        | 33  |      |

|                                | ENBL1, ENBL2, DDR, TRIP1, TRIP2     | -0 | .1     | 28  |      |

|                                | OUT1_U, OUT2_U                      | -0 | .8     | 33  |      |

|                                | OUT1_U, OUT2_U (with respect to LL) | -0 | .1     | 5.5 |      |

|                                | LL1, LL2                            | -0 | .8     | 28  | V    |

| I/O Voltage                    | REF_X                               | -0 | .1     | 12  |      |

|                                | SSTRT1, SSTRT2, COMP1, COMP2        |    | .1     | 5.5 |      |

|                                | SKIP, INV1, INV2                    | -0 | .1     | 5.5 |      |

|                                | PGOOD VO1_VDDQ, VO2                 | -0 | .1     | 5.5 |      |

|                                | OUT1_D, OUT2_D, VREG5               | -0 | .1     | 5.5 |      |

| 0                              | VREG5                               |    |        | 60  |      |

| Source current                 | REF_X                               |    |        | 5   | mA   |

| Operating free-air temperation | ure, T <sub>A</sub>                 | -4 | )      | 85  | °C   |

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to Absolute Maximum Rated conditions for extended periods may affect device reliability

#### **DISSIPATION RATING TABLE**

| PACKAGE    | T <sub>A</sub> < 25°C<br>POWER RATING | DERATING<br>FACTOR ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 85°C<br>POWER RATING |

|------------|---------------------------------------|------------------------------------------------|---------------------------------------|

| 30-pin DBT | 874 mW                                | 7.0 mW/°C                                      | 454 mW                                |

### **TPS51020**

SLUS564C - JULY 2003 - REVISED OCTOBER 2008

#### **ELECTRICAL CHARACTERISTICS**

$T_{A} = -40^{\circ}C \text{ to } 85^{\circ}C, 4.5 \text{ V} < \text{V}_{IN} < 20 \text{ V}, C_{VIN} = 0.1 \text{ } \mu\text{F}, C_{VREG5} = 2.2 \text{ } \mu\text{F}, C_{REF} \text{ } x = 0.01 \text{ } \mu\text{F}, \text{PGOOD} = 0.2 \text{ } \text{V}, \text{ENBLx} = \overline{\text{DDR}} = \text{VIN}, \text{INVx} = \text{COMPx}, \text{RSSTRTx} = \text{OPEN}, \text{TRIP1} = \text{TRIP2} = \text{VIN}, \text{LLx} = \text{GND}, \text{VBSTx} = \text{LLx+5}, C_{(OUTx\_U, OUTx\_D)} = 1 \text{ } \text{nF}, \text{REG5}_{\text{IN}} = 0 \text{ } \text{V}, \text{GND} = \text{OUTGNDx} = 0 \text{ } \text{V}, \text{VO1}_{\text{VDDQ}} = \text{VO2} = 0 \text{ } \text{V} \text{ (unless otherwise stated)}$

|                         | PARAMETER                                                    | TEST CONDITIONS                               |                                                    |      | TYP  | MAX  | UNIT |  |

|-------------------------|--------------------------------------------------------------|-----------------------------------------------|----------------------------------------------------|------|------|------|------|--|

| INPUT CURR              | NPUT CURRENTS                                                |                                               |                                                    |      |      |      |      |  |

| I <sub>VIN</sub>        | VIN supply current                                           | REG5V_IN = OPEN,<br>OSC = OFF                 | TRIPx = VIN,                                       |      | 1.4  | 2.2  | mA   |  |

| IVIN(STBY)              | VIN standby current                                          | ENBLx = 0 V,<br>REG5V_IN = OPEN,              | DDR = VIN,<br>OSC = OFF                            |      | 350  | 550  |      |  |

| I <sub>VIN</sub> (SHDN) | VIN shutdown current                                         | ENBLx = DDR = 0 V,<br>REG5V_IN = OPEN         |                                                    |      | 0.05 | 1.00 | μA   |  |

| I <sub>VIN</sub> (REG5) | V <sub>IN</sub> supply current, REG5_IN as 5-V input current | REG5V_IN = 5 V,                               | OSC = OFF                                          |      | 200  | 500  |      |  |

| IREG5                   | REG5_IN input supply current                                 | REG5V_IN = 5 V,                               | OSC = OFF                                          |      | 1.0  | 1.7  | mA   |  |

| IVBSTx                  | VBST supply current                                          | ENBLx = DDR = VIN                             |                                                    |      | 0.05 | 1.00 |      |  |

| IVBSTx                  | VBST shutdown current                                        | ENBLx = DDR = 0 V                             |                                                    |      | 0.05 | 1.00 | μA   |  |

| VREG5 INTE              | RNAL REGULATOR                                               |                                               |                                                    |      |      |      |      |  |

| VVREG5                  | VREG5 voltage                                                | IOUT = 0 A                                    |                                                    | 4.8  | 5.0  | 5.2  | V    |  |

| V <sub>LD5</sub>        | Load regulation                                              | $0 \text{ mA} \le I_{OUT} \le 50 \text{ mA},$ | V <sub>IN</sub> = 12 V                             |      | 0.6% | 2.5% |      |  |

| V <sub>LN5</sub>        | Line regulation                                              | I <sub>OUT</sub> = 20 mA,                     | $7 \text{ V} \leq \text{V}_{IN} \leq 28 \text{ V}$ |      | 0.4% | 2.0% |      |  |

| VTHL                    | UVLO threshold voltage                                       | High to low                                   |                                                    | 3.45 | 3.65 | 3.85 | V    |  |

| VHYS(UV)                | UVLO hysteresis                                              |                                               |                                                    | 100  | 200  | 300  | mV   |  |

| VTH(SW)                 | Switchover voltage                                           | REG_IN voltage                                |                                                    | 4.2  | 4.5  | 4.8  | V    |  |

| VHYS(SW)                | Switchover hysteresis                                        |                                               |                                                    | 50   |      | 250  | mV   |  |

SLUS564C - JULY 2003 - REVISED OCTOBER 2008

**ELECTRICAL CHARACTERISTICS (continued)**   $T_A = -40^{\circ}C$  to 85°C, 4.5 V < V<sub>IN</sub> < 20 V, C<sub>VIN</sub> = 0.1  $\mu$ F, C<sub>VREG5</sub> = 2.2  $\mu$ F, C<sub>REF\_X</sub> = 0.01  $\mu$ F, PGOOD = 0.2 V, ENBLx = DDR = VIN, INVx = COMPx, RSSTRTx = OPEN, TRIP1 = TRIP2 = VIN, LLx = GND, VBSTx = LLx+5, C<sub>(OUTx\_U</sub>, OUTx\_D)=1 nF, REG5\_IN = 0V, GND = 0.2 V, COUTx\_D, COUTx\_D) = 0.2 V, COUTx\_D = 0.2 V, C OUTGNDx = 0 V, VO1\_VDDQ = VO2 = 0 V (unless otherwise stated)

|                      | PARAMETER                                              | TEST CONDI                                                                     | TIONS                      | MIN  | TYP  | MAX   | UNIT       |

|----------------------|--------------------------------------------------------|--------------------------------------------------------------------------------|----------------------------|------|------|-------|------------|

| REF_X REFE           | RENCE VOLTAGE                                          |                                                                                |                            |      |      |       |            |

| VREF10               | 10-V reference voltage                                 | V <sub>IN</sub> = 14 V,                                                        | IOUT = 0 A                 | 8.5  | 10.0 | 11.0  | V          |

| V <sub>LD10</sub>    | Load regulation                                        | $0 \text{ mA} \leq I_{OUT} \leq 2 \text{ mA},$                                 | V <sub>IN</sub> = 18 V     |      | -12% | -20%  |            |

| VLN10                | Line regulation                                        | lout = 100 μA,                                                                 | 14 V≤V <sub>IN</sub> ≤28 V |      |      | 5%    |            |

| VREFVTT              | VTT reference voltage                                  | $\overline{\text{DDR}} = 0 \text{ V wrt VO1_VDDQ}$<br>V <sub>VO1</sub> = 2.5 V | input divided by 2         |      |      | 1.5%  |            |

| VREFVTT              | VTT reference load regulation                          | $0 \text{ mA} \le I_O \le 3 \text{ mA}$                                        |                            |      |      | 0.75% | 1          |

|                      | D COMPARATORS                                          | •                                                                              |                            |      |      |       |            |

|                      |                                                        | Undervoltage PGOOD                                                             |                            | 765  | 786  | 808   |            |

| VTHDUAL(PG)          | PGOOD threshold (dual mode)                            | Overvoltage PGOOD                                                              |                            | 892  | 920  | 945   | mV         |

|                      |                                                        | Undervoltage PGOOD,<br>VO1_VDDQ = 2.5 V                                        |                            | 1.12 | 1.14 | 1.16  |            |

| VTHDDR(PG)           | PGOOD threshold (DDR)                                  | Overvoltage PGOOD,<br>VO1_VDDQ = 2.5 V                                         |                            | 1.28 | 1.31 | 1.33  | V          |

| T <sub>PG(del)</sub> | PGOOD delay time                                       | INVx > undervoltage PGO0<br>Delay time from SSTRTx ><br>going high             |                            |      | 2048 |       | clks       |

| DIGITAL CON          | ITROL INPUTS                                           | -                                                                              |                            |      |      |       | -          |

| VIH                  | High-level input voltage, logic                        | DDR, ENBL1, ENBL2, SKI                                                         | P                          | 2.2  |      |       |            |

| VIL                  | Low-level input voltage, logic                         | DDR, ENBL1, ENBL2, SKIP                                                        |                            |      |      | 0.3   | V          |

| INLEAK               | Logic input leakage current                            | DDR, ENBL1, ENBL2, SKI                                                         | P= 5 V                     |      |      | 1.0   | μA         |

| VO1_VDDQ a           | and VO2                                                |                                                                                |                            |      |      |       | -          |

| RVOUT                | VOx sink impedance                                     | V <sub>VOUTx</sub> = 0.5 V, fault er                                           | ngaged                     |      | 6    | 10    | Ω          |

| VVOUTOK              | VOx low restart voltage                                | Fault condition removed, re                                                    | estart                     | 0.25 | 0.32 | 0.40  | V          |

| V <sub>VO2LEAK</sub> | VOx input leakage current                              | DDR= VIN,                                                                      | VOx = 5 V                  |      |      | 1.0   | μΑ         |

| R <sub>VOUT</sub>    | VO1_VDDQ input impedance                               | DDR= 0                                                                         |                            |      | 1.5  |       | MΩ         |

| UNDERVOLT            | AGE AND OVERVOLTAGE PROTECTION                         | •                                                                              |                            |      |      |       |            |

| VOVPDUAL             | OVP trip output threshold (dual)                       | Sensed at INVx                                                                 |                            | 945  | 970  | 1010  | mV         |

| VOVPDDR              | OVP trip output threshold (DDR)                        | VO1_VDDQ = 2.5 V                                                               |                            | 1.31 | 1.36 | 1.41  | V          |

| TOVP(del)            | OVP propagation delay time <sup>(1)</sup>              |                                                                                |                            |      | 20   |       | μs         |

| VUVPDUAL             | UVP trip output threshold (dual)                       | Sensed at INVx                                                                 |                            | 510  | 553  | 595   |            |

| VUVPDDR              | UVP trip output threshold (DDR)                        | VO1_VDDQ = 2.5 V                                                               |                            | 750  | 813  | 875   | mV         |

| TUVP(del)            | UVP propagation delay time                             |                                                                                |                            |      | 4096 |       | clks       |

| OVERCURRE            | ENT and INPUT VOLTAGE UVLO PROTECTIO                   | )N                                                                             |                            |      |      |       |            |

| ITRIPSNK             | TRIPx sink current                                     | $V_{TRIPx} = V_{IN} - 100 \text{ mV},$                                         | T <sub>A</sub> = 25°C      | 11   | 13   | 15    |            |

| ITRIPSRC             | TRIPx source current                                   | V <sub>TRIPx</sub> = 100 mV,                                                   | T <sub>A</sub> = 25°C      | 10   | 13   | 16    | μA         |

| TCITRIP              | TRIP current temperature coeficient <sup>(1)</sup>     | T <sub>A</sub> = 25°C                                                          |                            |      | 4200 |       | ppm/<br>°C |

| VOCPHI               | High-level OCP comparator offset voltage(1)            |                                                                                |                            |      | 0    | 3.0   |            |

| VOCPLO               | Low-level OCP comparator offset voltage <sup>(1)</sup> |                                                                                |                            |      | 0    | 5.0   | mV         |

| VVINUVLO             | VIN UVLO trip threshold                                | REF5V_IN = 4.8 V                                                               |                            | 3.7  | 3.9  | 4.1   | V          |

| VINHYS               | VIN UVLO trip hysteresis                               |                                                                                |                            | 100  | 200  | 300   | mV         |

#### **ELECTRICAL CHARACTERISTICS (continued)**

|                     | PARAMETER                                                 | TEST CONDITIONS                            |              | MIN  | TYP  | MAX   | UNIT |

|---------------------|-----------------------------------------------------------|--------------------------------------------|--------------|------|------|-------|------|

| 0.85-V REFE         | RENCE CONTROL LOOP                                        | •                                          |              | -    |      |       |      |

| V <sub>REFCH1</sub> | Error amplifier reference, channel 1 initial accuracy     | Measure COMP1,<br>T <sub>A</sub> = 25°C    | COMP1= INV1, | 0.84 | 0.85 | 0.86  | V    |

| V <sub>REFTC1</sub> | Error amplifier reference, channel 1 change with accuracy |                                            |              |      | 0.5% |       |      |

| VREFLN1             | Error amplifier reference, channel 1<br>change with line  |                                            |              |      | 0.1% |       |      |

| VCHMM               | Channel 2 to channel 1 voltage mismatch                   |                                            |              |      | 0    | 5.0   | mV   |

| CONTROL L           | OOP: SKIP HYSTERSTIC COMPARATOR AN                        | D ZERO CURRENT COM                         | PARATOR      |      |      |       |      |

| VLLHYS              | Skip hysteresis comparator hysteresis <sup>(1)</sup>      |                                            |              | 1    | 2    | 3     |      |

| VLLOFF              | Lload hysteresis comparator offset <sup>(1)</sup>         |                                            |              |      | 0    | 1     | mV   |

| VZOFF               | Zero current comparator offset <sup>(1)</sup>             |                                            |              |      | 10   | 18    | 1    |

| THLTOLL             | PWM skip delay time                                       |                                            |              |      | 8    |       |      |

| THLTOHL             | Skip to PWM delay time                                    |                                            |              |      | 1    |       | clks |

| CONTROL L           | OOP ERROR AMPLIFIER                                       |                                            |              |      |      |       |      |

| IEASRC              | COMPx source current                                      |                                            |              | 0.2  | 0.9  |       |      |

| IEASNK              | COMPx sink current                                        |                                            |              | 0.2  | 0.7  |       | mA   |

| FUGB                | Unity gain bandwidth <sup>(1)</sup>                       |                                            |              |      | 2.5  |       | MHz  |

| A <sub>OL</sub>     | Open loop gain <sup>(1)</sup>                             |                                            |              |      | 80   |       | dB   |

| CMRCOMP             | COMPx voltage range <sup>(1)(6)</sup>                     |                                            |              | 0.4  | VF   | EG5-3 | V    |

| INVLEAK             | INVx input current                                        |                                            |              |      |      | 0.5   | μΑ   |

| CONTROL L           | OOP: DUTY CYCLE, VOLTAGE RAMP, CHAN                       | INEL PHASE AND PWM D                       | ELAY PATH    |      |      |       |      |

|                     |                                                           | $f_{OSC} = 270 \text{ kHz}^{(3)}$          |              | 86%  | 88%  |       |      |

| DCMAX               | Maximum duty cycle                                        | fOSC = 360 kHz                             |              | 84%  | 85%  |       |      |

|                     |                                                           | $f_{OSC} = 450 \text{ kHz}^{(2)}$          |              | 80%  | 82%  |       |      |

| PHCH                | Channel to channel phase difference <sup>(5)</sup>        | PWM phase reversal only                    | у            |      | 180  |       | 0    |

| T <sub>MIN</sub>    | OUTX_U minimum pulse width <sup>(1)</sup>                 |                                            |              |      | 100  |       | ns   |

| TIMERS: INT         | ERNAL OSCILLATOR <sup>(4)</sup>                           |                                            |              |      |      |       |      |

| fOSC(hi)            | Fast oscillator frequency initial accuracy <sup>(2)</sup> | R <sub>SSTRTx</sub> = OPEN                 |              |      | 450  |       |      |

| fOSC(lo)            | Slow oscillator frequency initial accuracy                | $R_{SSTRTx} = 1M\Omega \text{ or } V_{SS}$ | STRT = 3 V   |      | 270  |       | kHz  |

| fOSC(tc)            | Oscillator frequency over line and temperature            | Trimmed for 360 kHz                        |              | 306  | 360  | 414   | 1    |

(1) Ensured by design. Not production tested.

(2) Maximum 450-kHz frequency can be achieved when both channels are enabled.

(3) 270 kHz is the default frequency during start-up for both channels.

(4) See Table 1.

(5) See PWM detailed description

SLUS564C - JULY 2003 - REVISED OCTOBER 2008

#### **ELECTRICAL CHARACTERISTICS (continued)**

$T_{A} = -40^{\circ}C \text{ to } 85^{\circ}C, 4.5 \text{ V} < \text{V}_{\text{IN}} < 20 \text{ V}, C_{\text{VIN}} = 0.1 \text{ } \mu\text{F}, C_{\text{VREG5}} = 2.2 \text{ } \mu\text{F}, C_{\text{REF}} x = 0.01 \text{ } \mu\text{F}, \text{PGOOD} = 0.2 \text{ V}, \text{ENBLx} = \overline{\text{DDR}} = \text{VIN}, \text{INVx} = \text{COMPx}, \text{RSSTRTx} = \text{OPEN}, \text{TRIP1} = \text{TRIP2} = \text{VIN}, \text{LLx} = \text{GND}, \text{VBSTx} = \text{LLX+5}, C_{(\text{OUTx}U, \text{OUTx}D)} = 1 \text{ } n\text{F}, \text{REG5}_{\text{IN}} = 0\text{ } \text{V}, \text{GND} = \text{OUTGNDx} = 0 \text{ V}, \text{VO1}_{\text{VDDQ}} = \text{VO2} = 0 \text{ V} \text{ (unless otherwise stated)}$

|                   | PARAMETER                                      | TEST CONDITIONS                                                              | MIN  | TYP  | MAX  | UNIT |

|-------------------|------------------------------------------------|------------------------------------------------------------------------------|------|------|------|------|

| TIMERS: SO        | -                                              |                                                                              |      | P    |      |      |

| ISSQ              | SSTRTx charge current                          | V <sub>SSTRTx</sub> = 1 V                                                    | 1.8  | 2.3  | 2.9  | μΑ   |

| ISSDQ             | SSTRTx discharge current                       | V <sub>SSTRTx</sub> = 0.5 V                                                  | 0.1  |      |      | mA   |

| VREFTRK           | SSTRTx at SMPS regulation point voltage(7)     |                                                                              | 1.00 | 1.22 | 1.45 |      |

| VSSOK             | SSTRTx OK to restart voltage                   |                                                                              | 0.23 | 0.29 | 0.35 |      |

| VSSFIN            | SSTRTx finished voltage <sup>(8)</sup>         |                                                                              | 1.4  | 1.5  | 1.6  | V    |

| VSSCLP            | SSTRTx frequency select voltage <sup>(9)</sup> |                                                                              | 3.35 | 3.60 | 3.80 |      |

| OUTPUTS: I        | NTERNAL BST DIODE                              | •                                                                            |      |      |      |      |

| V <sub>FBST</sub> | Forward voltage                                | $(V_{VREF5} - V_{VBSTx})V_{VREF5} = 5 V, I_F = 10 mA$<br>$T_A = 25^{\circ}C$ |      | 0.80 | 0.85 | V    |

| IRBST             | Reverse current                                | V <sub>RBST</sub> = 30 V                                                     |      | 0.1  | 0.5  | μA   |

| OUTPUTS: N        | N-CHANNEL MOSFET GATE DRIVERS                  | •                                                                            |      |      |      |      |

| RUSRC             | OUTx_U source impedance                        |                                                                              |      | 3    | 10   |      |

| RDSRC             | OUTx_D source impedance                        |                                                                              |      | 3    | 10   |      |

| RUSNK             | OUTx_U sink impedance                          |                                                                              |      | 2.5  | 5.0  | Ω    |

| RDSNK             | OUTx_D sink impedance                          |                                                                              |      | 2.5  | 5.0  |      |

| TDEAD             | Gate non-overlap dead time                     |                                                                              |      | 100  |      | ns   |

(1) Ensured by design. Not production tested.

(2) Maximum 450-kHz frequency can be achieved only when both channels are enabled.

(3) 270 kHz is the default frequency during start-up for both channels.

(4) See Table 1.

(5) See PWM detailed description

(6) Feedforward Gain can be approximated as follows:

VRAMP= K1×VIN+B1, VOFFSET=K2×VIN×+B2 where K1=0.017, K2=0.01, B1=0.35 V, B2=0.4 V.

At the running duty cycle, the V<sub>COMP</sub> should be approximately:  $V_{COMP} = V_{OUT} \times \left(K1 + \frac{B1}{VIN}\right) + (K2 \times VIN + B2)$

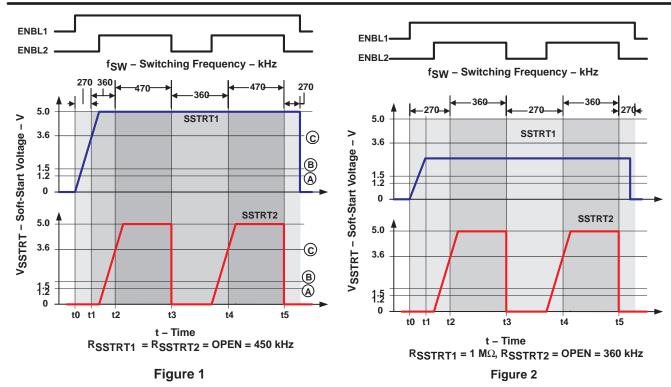

(7) See waveform point A in Figure 1

(8) See waveform point B in Figure 1

(9) See waveform point C in Figure 1

#### Table 1. Frequency Selection

| SSTRT1                            | SSTRT2                                  | FREQUENCY (kHz) |  |  |

|-----------------------------------|-----------------------------------------|-----------------|--|--|

| C <sub>SSTRT</sub> only           | C <sub>SSTRT</sub> only                 | 450(10)         |  |  |

| 1 MΩ    C <sub>SSTRT</sub> to GND | C <sub>SSTRT</sub> only                 | 360             |  |  |

| C <sub>SSTRT</sub> only           | 1 M $\Omega \parallel C_{SSTRT}$ to GND | 360             |  |  |

| 1 MΩ    C <sub>SSTRT</sub> to GND | 1 M $\Omega \parallel C_{SSTRT}$ to GND | 270             |  |  |

(10)Although selection is made by placing a 1M resistor in parallel with the SSTRTx timing capacitor, the softstart time to 0.85V is altered by about only 20%.

## **TPS51020**

SLUS564C - JULY 2003 - REVISED OCTOBER 2008

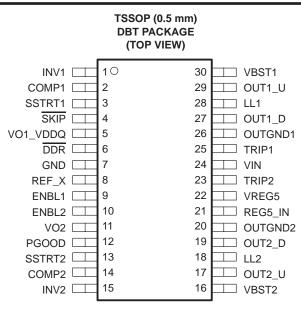

#### **TERMINAL FUNCTIONS**

| TERMINAL I/O |     |     | DECODIDION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME         | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| COMP1        | 2   | 0   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| COMP2        | 14  | 0   | Error amplifier output. Connect feedback network to this pin and INVx for compensation of control loop.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| DDR          | 6   | I   | DDR selection pin. If this pin is grounded, the device runs in DDR Mode. The error amplifier reference for VO2 is (VO1_VDDQ)/2, the REF_X output voltage becomes (VO1_VDDQ)/2 and skip mode is disabled for VO2, Also, VREG5 is turned off when both ENBLx are at low in this mode. If this pin is at 2.2-V or higher, the device runs in ordinary dual SMPS mode (dual mode), then the error amplifier reference for VO2 is connected to internal 0.85-V reference, the REF_X output voltage becomes 10 V, VREG5 is kept on regardless of ENBLx status. <b>CAUTION: Do not toggle DDR while ENBL1 or ENBL2 are high.</b> (See Table 2) |

| ENBL1        | 9   | Ι   | TTL Enable Input. If ENBLx is greater than 2.2 V, then the VREG5 is enabled (DDR mode) and the SMPS of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| ENBL2        | 10  | I   | that channel attempts to turn on. If both ENBL1 and ENBL2 are low then the 10-V (or (VO1_VDDQ)/2 output) voltage as well as the oscillator are turned off. (See Table 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| GND          | 7   | 0   | Signal ground pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| INV1         | 1   | Ι   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| INV2         | 15  | Ι   | Error amplifier inverting input. Also input for skip comparator, and OVP/UVP comparators.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| LL1          | 28  | I/O |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| LL2          | 18  | I/O | Switch-node connection for high-side driver and overcurrent protection circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| OUT1_D       | 27  | 0   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| OUT2_D       | 19  | 0   | Synchronous N-channel MOSFET driver output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| OUT1_U       | 29  | 0   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| OUT2_U       | 17  | 0   | High-side N-channel MOSFET driver output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| OUTGND1      | 26  | 0   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| OUTGND2      | 20  | 0   | Ground return for OUTx_D.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

#### **TERMINAL FUNCTIONS (continued)**

| TERMINAL |          |     | DECODIDITION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------|----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME     | NO.      | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PGOOD    | 12       | 0   | Power good output. This is an open drain pull-down pin for power good. It remains low during soft-start until both outputs become within $\pm$ 7.5%. If INV1 or INV2 is out of regulation, or VREG5V goes under UVLO then this pin goes low. The internal delay timer counts 2048 clks at low to high (by design, no delay for high to low). If ENBLx is low, and the power good output is high, then the power good signal for that channel is ignored.                                        |

| REF_X    | 8        | 0   | 10-V N-channel MOSFET bias or (VO1_VDDQ)/2 reference output. If dual mode is selected ( $\overline{\text{DDR}} > 2.2 \text{ V}$ ) then this pin provides a low 10-V current (< 2 mA) bias, dropped down from V <sub>IN</sub> , for the SO – S5 switched N-channel MOSFETs. If DDR mode is selected ( $\overline{\text{DDR}} = \text{GND}$ ) then this pin becomes (VO1_VDDQ)/2 capable of 3 mA source current. This bias/reference is shut off when ENBL1 and ENBL2 are both low. (See Table 2) |

| REG5_IN  | 21       | Ι   | External 5V regulator Input. If this pin is above 4.7 V, then the 5 V circuit bias switches from the VREF5 to the supply presented to REG5_IN.                                                                                                                                                                                                                                                                                                                                                  |

| SSTRT1   | 3        | Ι   | Soft-start/frequency select input. Connect a capacitor between SSTRTx and ground for adjusting the softstart time. A constant current fed to this capacitor ramps the reference during startup. Frequency selection is de-                                                                                                                                                                                                                                                                      |

| SSTRT2   | 13       | Ι   | scribed in Table 1. The soft-start capacitor is discharged upon UVLO/OVP/UVP, or when ENBLx is asserted low.                                                                                                                                                                                                                                                                                                                                                                                    |

| SKIP     | 4        | I   | Skip mode selection pin. Ground for automatic control between PWM mode in heavy load and hysteretic operation in light load. Tie high for PWM only operation for the entire load condition. If DDR is grounded, then skip mode is disabled for Channel 2.                                                                                                                                                                                                                                       |

| TRIP1    | 25       | I   | Channel 1 overcurrent trip point voltage input. Connect a resistor between TRIP1 and the high-side N-channel MOSFET input conversion voltage for high-side N-channel MOSFET UVP current limit shut down. Connect resistor between TRIP1 and GND for low-side N-channel MOSFET overcurrent latch shutdown.                                                                                                                                                                                       |

| TRIP2    | 23       | I   | Channel 2 overcurrent trip point voltage input. Connect a resistor between TRIP2 and the high-side N-channel MOSFET input conversion voltage for high-side N-channel MOSFET UVP current limit shut down with a 180° channel phase shift. Connect resistor between TRIP2 and GND for low-side N-channel MOSFET over current latch shut-down. The oscillator voltage ramp adjustment (the feed-forward feature) for channel 2 is disabled when this pin is tied to ground via a resistor.         |

| VBST1    | 30       | Ι   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| VBST2    | 16       | Ι   | Supply Input for high-side N-channel FET driver. Typically connected via charge pump from LLx.                                                                                                                                                                                                                                                                                                                                                                                                  |

| VO1_VDDQ | 5        | Ι   | Output discharge pin. Connect this pin to the SMPS output. The output is discharged to at least 0.3 V before                                                                                                                                                                                                                                                                                                                                                                                    |

| VO2      | VO2 11 I |     | the channel can start-up again. If DDR is low, then the VO1_VDDQ pin must be connected to the VDDQ output since this pin works as the VDDQ feedback to generate the VTT reference voltage and VO2 should be connected to GND since V <sub>TT</sub> must remain in a high-impedance state during S3 mode.                                                                                                                                                                                        |

| VREG5    | 22       | 0   | Internal, 60-mA, 5-V regulator output. DDR, ENBL1 or ENBL2 high ( > 2.2V) turns on the 5 V regulator.                                                                                                                                                                                                                                                                                                                                                                                           |

| VIN      | 24       | I   | High-voltage input. Typically the battery voltage. This pin serves as inputs for the VREF5 regulator, the REF_X regulator and positive input for overcurrent comparators. Precaution should be taken for tracing between this pin and the high-side N-channel MOSFET drain where positive node of TRIPx resistors are located.                                                                                                                                                                  |

#### Table 2. Reference Regulator Control

| MODE | DDR  | ENBL1 | ENBL2 | VREF5 | REF_X   | OSC |

|------|------|-------|-------|-------|---------|-----|

| DDR  | LOW  | LOW   | LOW   | OFF   | OFF     | OFF |

| DDR  | LOW  | LOW   | HIGH  | ON    | OFF     | ON  |

| DDR  | LOW  | HIGH  | LOW   | ON    | VO1_DDR | ON  |

| DDR  | LOW  | HIGH  | HIGH  | ON    | VO1_DDR | ON  |

| DUAL | HIGH | LOW   | LOW   | ON    | OFF     | OFF |

| DUAL | HIGH | LOW   | HIGH  | ON    | 10 V    | ON  |

| DUAL | HIGH | HIGH  | LOW   | ON    | 10 V    | ON  |

| DUAL | HIGH | HIGH  | HIGH  | ON    | 10 V    | ON  |

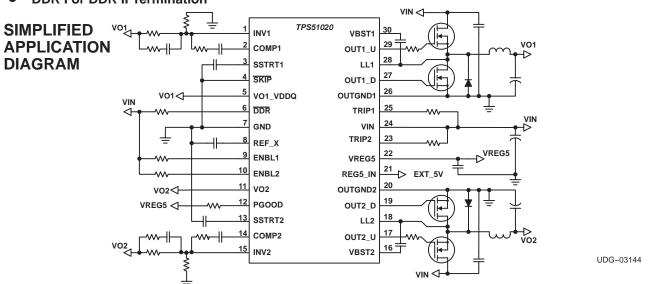

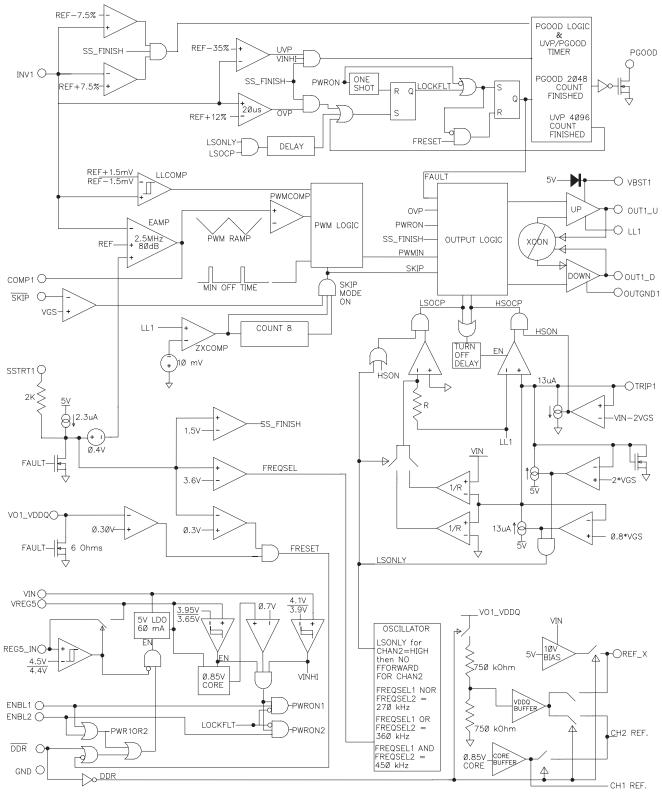

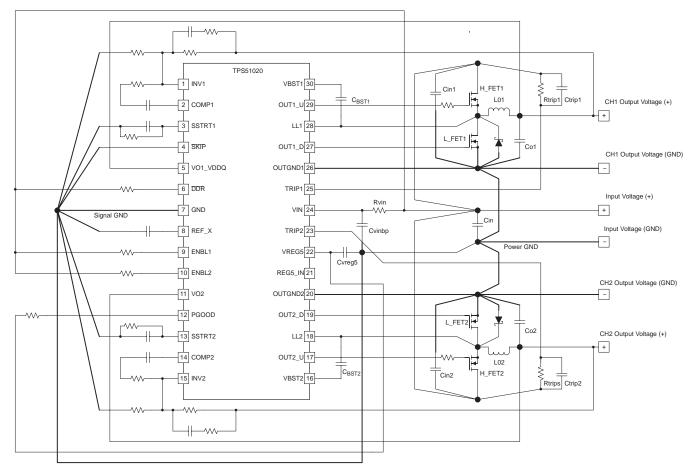

#### FUNCTIONAL BLOCK DIAGRAM

Shows Channel 1 (VO1\_VDDQ) and the supporting circuitry.

#### **PWM OPERATION**

The PWM control block utilizes a fixed-frequency, feed-forward, voltage-mode control scheme with a wide-bandwidth, low-impedance output error amplifier as the voltage servo control block. This scheme allows the highest efficiency down conversion while maintaining excellent line regulation and fast transient response. Loop compensation is programmed by connecting a filter network between the COMPx pin and the INVx pin. The wide bandwidth error amplifier handles conventional Type II compensation or Type III compensation when using ceramic capacitors for the converter output. For channel one, the reference signal for the control loop is always a precision 0.85-V internal reference, while the channel two loop reference is either the 0.85-V reference or, in the case of DDR mode, one half the VO1\_VDDQ voltage, (VO1\_VDDQ)/2. The output signal of the error amplifier appears at the COMPx pin and is compared to a buffered version of the 0.6-V oscillator ramp. When TRIP2 pin is tied to VIN through a resistor, the voltage ramp is further modulated by the input voltage, VIN, to maintain a constant modulator gain. If the TRIP2 pin is connected to ground through a resistor, then the voltage ramp remains fixed regardless of VIN value.

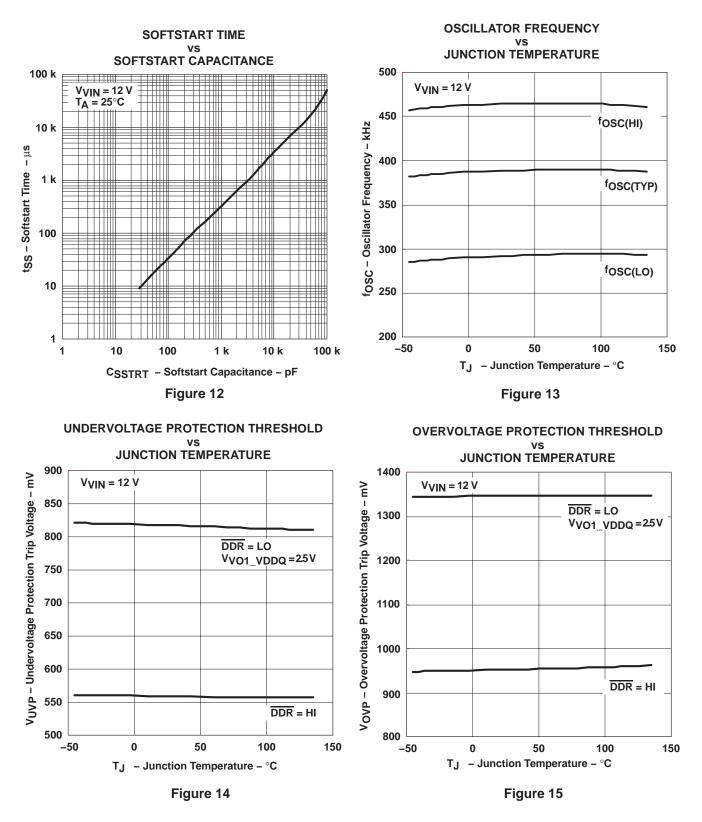

The oscillator frequency is internally fixed and can be selected at 270 kHz, 360 kHz or 470 kHz by insertion of a clamping resistor on the SSTRTx pin per Table 1. For example, 470 kHz can be attained when both SSTRTx voltages exceed 3.5 V, as described in WAVEFORM1. The controller begins with 270 kHz in the first stage of the softstart, and then increases to 470 kHz at the steady state. When 270 kHz is selected, both of SSTRTx voltages are kept below 3.5 V so that the frequency is the same 270 kHz for the entire operation.

Two channels are operated in 180 degrees out-of-phase interleave switching mode. This interleaving helps reduce the input current ripple requirement for the input capacitor. However, because the PWM loop determines both the turn-off AND turn-on of the high-side MOSFET, this 180 degree operation may not be apparent by looking at the LLx nodes only. Rather, the turn-off cycle of one channel always corresponds to the turn-on cycle of the other channel and vise-versa. As a result, input ripple is reduced and dynamic response is improved over a broad input voltage range.

#### MAXIMUM DUTY CYCLE

Because most notebook applications typically run from three to four cell Li–lon or run from a 20-V adapter, 100% duty cycle operation is not required. Rather, the TPS51020 is optimized for low duty ratio step-down conversion. As a result of limiting the duty cycle, the flying BST capacitor is refreshed reliably and the low-side over current detection circuitry is capable of detecting an overcurrent condition even if the output is stuck between the regulation point and UVP. The maximum duty cycle for each operating frequency is 88% for 270 kHz, 85% for 360 kHz and 82% for 470 kHz.

It should be noted that if the system is operating close to maximum (or minimum) duty cycle, it may be difficult for the converter to respond quickly during line/load transients or state changes (such as frequency switching during soft start or PWM to SKIP mode transitions). This slow response is due to the dynamic range of the COMP pin and is usually not a result of poor phase compensation. In the case of minimum duty cycle operation, the slow response is due to the minimum pulse width of the converter (100 ns TYP). In this case (counter intuitively), it may be advisable to slow down the switching frequency of the converter in order to improve response time.

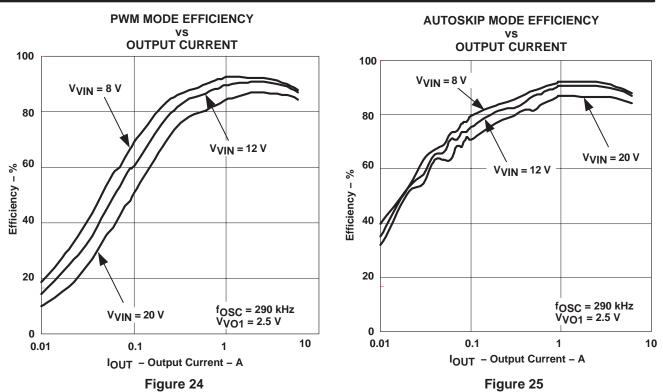

#### SKIP MODE OPERATION

If the SKIP pin is set HIGH, the SMPS operates in the fixed PWM mode. While a LOW signal is applied, the controller operates in autoskip mode. In the autoskip mode, the operation changes from constant frequency PWM mode to an energy-saving skip mode automatically by detecting the edge of discontinuous current mode. During the skip mode, the hysteretic comparator monitors output voltage to trigger high side on at the next coming oscillator pulse after the lower level is detected. Several sequential pulses may be seen, especially in the intermediate load level, before output capacitor is charged up to the higher level and waits for next cycle. In the skip mode, frequency varies with load current and input voltage.

Skip mode for SMPS\_2 is disabled regardless of the  $\overline{SKIP}$  pin status if DDR mode is selected (see *Dual Mode and DDR Mode* section). This is because current sink capability is required for V<sub>TT</sub>, so that rectifying MOSFET needs to be kept on when the inductor current flows inversely. SMPS\_1 is still capable of skip mode operation while DDR Mode.

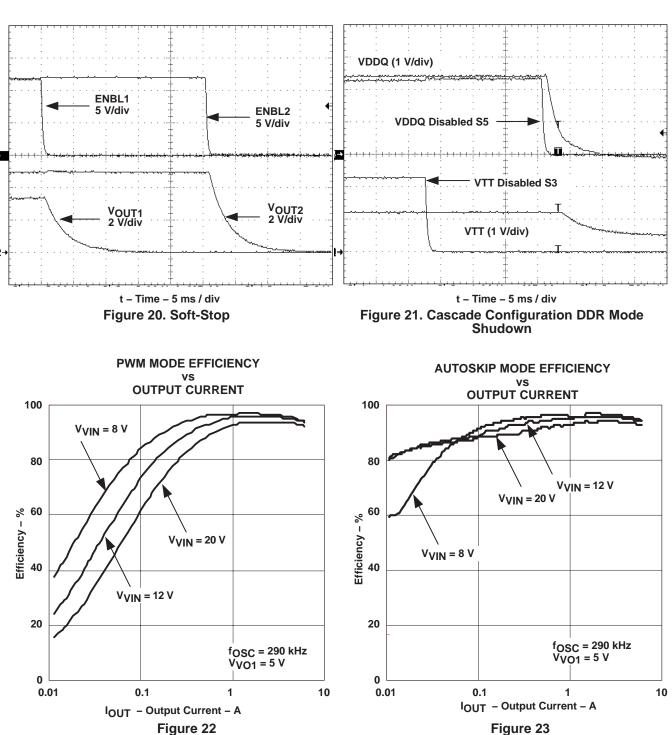

#### **CASCADE CONFIGURATION**

If the TRIP2 pin is tied through a resistor to the input voltage, the TPS51020 assumes that the conversion voltage for channel two is the VIN voltage, usually VBATT. Conversely, if TRIP2 is tied through a resistor to ground, the controller assumes that the conversion voltage for channel two is the output voltage of channel one or some other stable bus voltage.

#### DUAL MODE AND DDR MODE

TPS51020 provides one-chip solution for system power supply, such as for 5 V, 3.3 V or 1.8 V, and a dual switcher DDR power supply. By simply selecting  $\overline{\text{DDR}}$  signal and some external configuration change following the instructions below, TPS51020 gives a complete function set required for the DDR termination supply such as VDDQ/2 tracking V<sub>TT</sub> source/sink capability and V<sub>TT</sub> reference output.

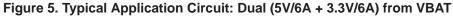

If  $\overline{\text{DDR}}$  is set high ( > 2.2 V), the TPS51020 runs in dual mode, that is, each converter produces an independent output voltage with respect to the internal 0.85-V reference. Bypass REF\_X to ground by 0.01-µF. The VO1\_VDDQ or VO2 terminal should be connected to their corresponding switcher output. The 10-V reference output can be used as FET switch biasing for power control during sleep states (see Figure 5). During this dual mode, selection of autoskip mode or PWM mode made by SKIP applies to both SMPS\_1 and SMPS\_2.

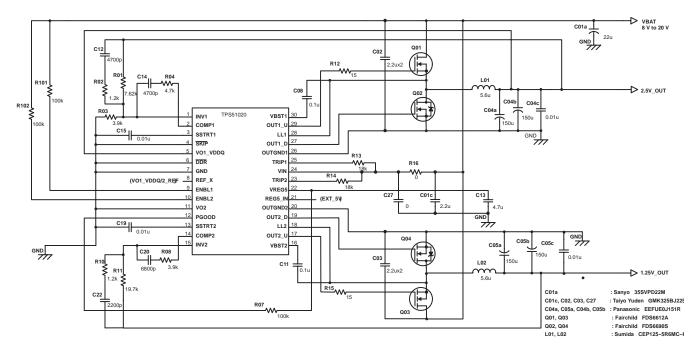

If DDR is set low ( < 0.3V), the TPS51020 operates as a dual switcher DDR supply; VDDQ from SMPS\_1 and V<sub>TT</sub> from SMPS\_2 (DDR Mode). In this mode, the reference voltage for SMPS\_2 is switched to (VO1\_VDDQ)/2 to track exactly half the voltage of SMPS\_1, divided by internal resistors. VO1\_VDDQ should be connected to SMPS\_1 output terminal to accomplish this. REF\_X outputs the (VO1\_VDDQ)/2 voltage after a buffer (5-mA max). SKIP controls only SMPS\_1 and SMPS\_2 is forced to operate in PWM mode so that current can be sink from the output. Power source of SMPS\_2 can either be the battery voltage (independent configuration), or the VDDQ (cascade configuration) by user's preference. When using the independent configuration, TRIP2 needs to be connected to the VIN node via trip resistor. In case of cascade configuration, tie TRIP2 to GND via trip resistor (see Figure 7).

CAUTION:Do NOT toggle  $\overline{DDR}$  HIGH while ENBL1 or ENBL2 is high (see Table 2). REF\_X output switches to high voltage (10 V) and be applied to V<sub>TTREF</sub> directly

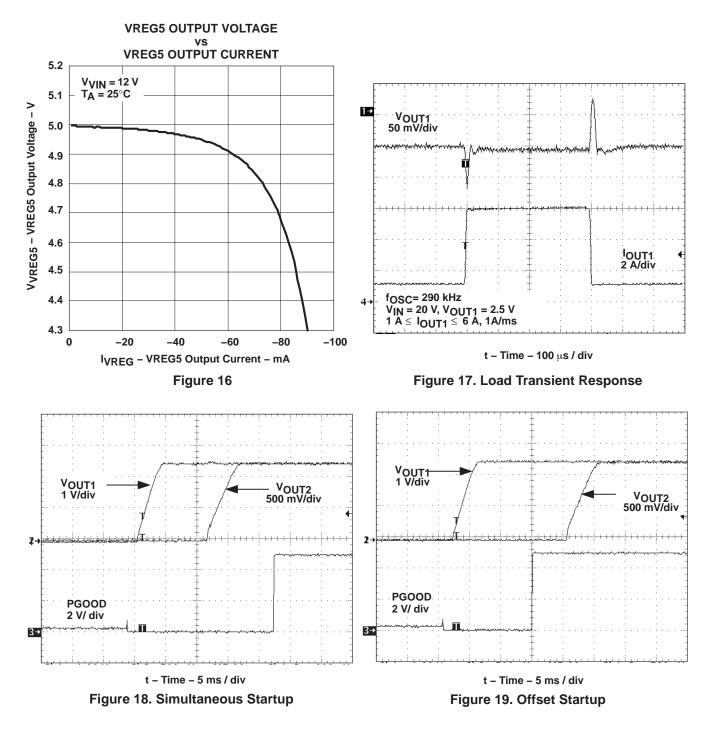

#### **5-V LINEAR REGULATOR (VREG5)**

The VREG5 voltage is the bias for all the low voltage circuitry in the TPS51020 as well as the DC boost voltage for the MOSFET gate drivers. Total available current is 60 mA. Bypass this pin to GND by 4.7- $\mu$ F. The under voltage lockout (UVLO) circuit monitors the output of this regulator to protect internal circuitry from low input voltages. If 5 V is applied to REG5\_IN from either the SMPS output or an alternate 5 V, then the linear regulator is turned off and the VREG5 pin is switched over to REG\_IN. This operation enhances the efficiency of the overall power supply system because the bulk of the quiescent current now runs from the 5-V output instead of VIN (VBAT). In this configuration, ensure that VREG5\_IN is less than or equal to V<sub>VIN</sub>.

#### EXTERNAL 5V INPUT (REG5\_IN)

When a 5-V bus is available, VIN does not need to be connected to the battery. In this configuration, VIN should be connected to REG5\_IN.

#### LOW-SIDE N-CHANNEL FET DRIVER

The low-side driver is designed to drive high current low  $R_{DS(on)}$  N-channel MOSFET(s). The maximum drive voltage is 5.5 V. The drive capability is represented by its internal resistance, which are 3  $\Omega$  for VREG5 to OUTx\_D and 2.5  $\Omega$  for OUTx\_D to OUTGNDx. A dead time is internally generated between top MOSFET off to bottom MOSFET on, and bottom MOSFET off to top MOSFET on, in order to prevent shoot through.

The low-side driver is typically turned off during all fault modes except for OVP. When an OVP condition exists, the low-side driver of the offending channel turns on and attempts to blow the protection fuse of the input supply.

#### **HIGH-SIDE N-CHANNEL FET DRIVER**

The high-side driver is designed to drive high current, low  $R_{DS(on)}$  N-channel MOSFET(s). When configured as a floating driver, a 5-V bias voltage is delivered from VREG5 supply. The instantaneous drive current is supplied by the flying capacitor between VBSTx and LLx pins, 0.1- $\mu$ F ceramic for typical applications. The boost diodes are integrated and are sufficient for enhancing the high-side MOSFET. However, external boost diodes can also be added from VREG5 to each VBSTx in case higher gate-to-source votlage is required.

The drive capability is represented by its internal resistance, which are as follows:  $3 \Omega$  for VBST to OUTx\_U and  $2.5 \Omega$  for OUTx\_U to LLx. The maximum voltage that can be applied between OUTx\_U pin and OUTGNDx pin is 35 V.

#### **ENABLE AND SOFT-START**

Each SMPS is switched into standby mode separately by grounding the corresponding ENBLx pin. The 5-V supply is enabled if either the DDR, ENBL1 or ENBL2 pin(s) goes high ( >2.2 V).

Softstart of each SMPS is achieved by slowly ramping the error amplifier reference voltage by following a buffered version of the SSTRTx pin voltage. Designers can achieve their own start-up sequencing by simply provide external timing signals since the startup times do not depend on the load current. The softstart time is programmable by external capacitor connected from SSTRTx pin to the ground. Each SSTRTx pin sources constant current, typically 2.3 µA. The output voltage of the SMPS ramps up from 0 V to its target regulation voltage as the SSTRTx pin voltage increases from 0 V to 1.2 V. This gives the softstart time formula to be,

$C_{SSTRT} (Farads) = \frac{T_{SSTRT} (sec) \times 2.3 \times 10^{-6}}{1.2}$

The soft-start capacitor is discharged upon UVLO, OVP or UVP is detected as well as ENBLx is set low.

#### **OUTPUT DISCHARGE (SOFT-STOP)**

When an SMPS is turned off by ENBLx asserted low or the part enters a fault mode, both top and bottom drivers are turned off. This may leave the output in a high impedance state that allows the voltage to persist for some time. Output voltage should be discharged prior to the next power up. To achieve this, connect the output to the VO1\_VDDQ or VO2 pins.

These pins turn on a 6- $\Omega$  resistor to ground during an off or fault condition. Both the VO1\_VDDQ and VO2 pin must be discharged to 0.3 V before the TPS51020 restarts. The TPS51020 has the flexibility of adding a resistor in series with the VOx pin and the output voltage in order to reduce the discharge current and reduce the total power dissipation within the device. It should be noted that when this resistor is added the discharged voltage threshold changes according to the following equation:

$$V_{\text{DISCHARGE}} = \frac{\left(R_{\text{EXTERNAL}} + R_{\text{DS(on)}}\right)}{R_{\text{DS(on)}}} \times 0.3$$

where

- R<sub>EXTERNAL</sub> is the series resistor between VOx and the output

- R<sub>DS(on)</sub> = 6 Ω

#### 10-V N-CHANNEL FET BIAS or (VOUT1)/2 VTT VOLTAGE REFERENCE (REF\_X)

TPS51020's REF\_X provides two functions depending on the operational mode. One is a linear regulator that supply 10-V for FET switch biasing in the dual mode, the other is  $V_{TT}$  reference voltage in the DDR mode.

If  $\overline{\text{DDR}}$  is high ( > 2.2 V) then the REF\_X output is a convenient 10-V, 2-mA (maximum) output, useful for biasing N-channel FET switches typically used to manage S0, S3 and S5 sleep states where the main supply is switched to many outputs. When V<sub>IN</sub> is < 12 V, REF\_X approximately tracks V<sub>IN</sub>-2 V.

If  $\overline{\text{DDR}}$  is low, then the REF\_X output becomes the VDDQ/2 (VO1\_VDDQ/2) reference. This output is capable of 5-mA source current and is left on even if channel two (V<sub>TT</sub> switcher) is turned off. REF\_X is turned off if ENBL1 and ENBL2 are both low (see Table 2).

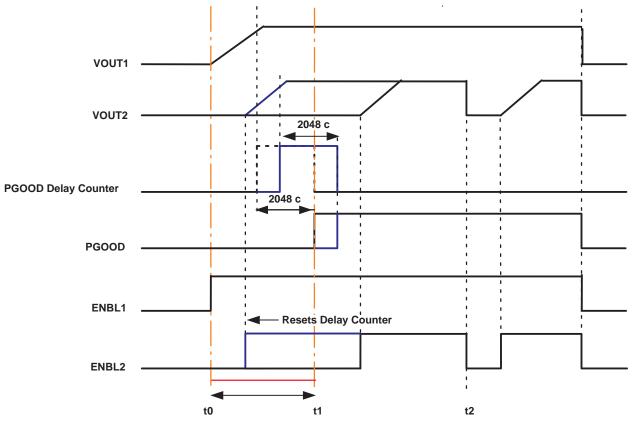

#### POWERGOOD

The TPS51020 has advanced powergood logic that allows single powergood circuit to monitor both SMPS output voltages (see Figure 3).

#### Figure 3. PowerGood Timing Diagram

The PGOOD terminal is an open drain output. The PGOOD pin remains low until both power supplies have started and have been in regulation ( $\pm$ 7.5%) for 2048 clock pulses.

If one channel is enabled in the period between T0 and T1, (the other channel's ramp time plus delay time,) the PGOOD delay counter restarts counting softstart finish after the last channel has finished softstart. Enabling after T1 is ignored by PGOOD until the channel finishes its softstart. If either of the SMPS output goes out by  $\pm$  7.5% or UVLO is detected while ENBLx is high, PGOOD pulls low. If a channel is disabled while the other is still active PGOOD maintains it's logic state and only monitor the active channel.

#### **PROTECTION FUNCTIONS**

The TPS51020 is equipped with input undervoltage lock out (UVLO), output undervoltage protection (UVP) and overvoltage (OVP) protection. Overcurrent is detected using  $R_{DS(on)}$  of the external power MOSFETs and protected by triggering UVP, or latch off in some cases. The states of output drive signal depends on which protection was involved. Please refer to each protection description below for the detail.

When the input voltage UVLO is tripped, the TPS51020 resets and waits for the voltage to rise up over the threshold voltage and restart the device. Alternatively, if output UVP or OVP is triggered, the device latches off after a delay time defined by the internal fault counter counting the PWM oscillator pulses. The VREF5 and REF\_X is kept on in this latch off condition. The fault latch can be reset by toggling both of ENBLx pins in DDR mode. The fault latch can be reset by either toggling VIN or bringing DDR, ENBL1 and ENBL2 all low. Be sure to bring DDR high prior to ENBLx when TPS51020 is being used in dual mode.

If a false trip of the UVLO appears due to input voltage sag during turn-on of the high-side MOSFET such as a large load transient, first consider adding several micro-farads of input capacitance close to the MOSFET's drain. Also consider adding a small V<sub>IN</sub> filter, ex. a 2.2- $\Omega$  resistor and a 2.2- $\mu$ F, for decoupling. The trip resistors should be connected to the same node as VIN pin of the device when this filter is applied. The filter resistor should be as small as possible since a voltage drop across this resistor biases the OCP trip point.

#### UNDERVOLTAGE LOCKOUT PROTECTION

There are two undervoltage lock out protections (UVLO) in TPS51020. One is for  $V_{IN}$ , which has a typical trip threshold voltage 3.9 V and trip hysteresis 200 mV. The other is for VREF5, which has a typical trip threshold voltage 3.65 V and trip hysteresis 300 mV. If either is triggered, the device resets and waits for the voltage to rise up over the threshold voltage and restart the part. Please note this protection function DOES NOT trigger the fault counter to latch off the part.

#### **OVERVOLTAGE PROTECTION**

For overvoltage protection (OVP), the TPS51020 monitors INVx voltage. When the INVx voltage is higher than 0.95V (+12%), the OVP comparator output goes high (after a 20-µs delay) and the circuit latches the top MOSFET driver OFF, and bottom driver ON for the SMPS detected overvoltage. In addition, the output discharge (softstop) function is enabled to discharge the output capacitor. The fault latch can be reset by either toggling VIN or bringing DDR, ENBL1 and ENBL2 all low. Be sure to bring DDR high prior to ENBLx when TPS51020 is being used in dual mode.

#### UNDERVOLTAGE PROTECTION

For undervoltage protection (UVP), the TPS51020 monitors INVx voltage. When the INVx voltage is lower than 0.55 V (-35 %), the UVP comparator output goes high, and the internal FLT timer starts to count PWM oscillator pulses. After 4096 clock pulses, the part latches off. Both top and bottom drivers are turned off at this condition. Output discharge (soft-stop) function is enabled to discharge the output capacitor. The fault latch can be reset by either toggling VIN or bringing DDR, ENBL1 and ENBL2 all low. Be sure to bring DDR high prior to ENBLx when TPS51020 is being used in dual mode.

#### **OVERCURRENT PROTECTION**

Overcurrent protection (OCP) is achieved by comparing the drain to source voltage of the high-side and low-side MOSFET to a set point voltage. This voltage appears at the TRIPx pin and is defined by the conversion voltage, typically VIN, minus the I  $\times$  R drop of the I<sub>TRIP</sub> current flowing through the external resistor connected to the conversion voltage. The offset of the internal comparators also plays a role in determining the overall accuracy and set point of the OCP limit.

When the drain-to-source voltage of the synchronous MOSFET exceeds the set point voltage created by the I×R drop (usually 20 mV to around 150 mV), the synchronous MOSFET on-time is extended into the next pulse and the high-side MOSFET OCP comparator is enabled. If during the subsequent high-side on-time the drain-to-source voltage of the high-side MOSFET exceeds the set point voltage, then the high-side on-time pulse is terminated. This low-side extension/high-side termination action has the effect of decreasing the output voltage until the UVP circuit is activated to turn off both the high-side and low-side drivers. The TPS51020 I<sub>TRIP</sub> current has a temperature coefficient of 4200 PPM/°C.

The threshold voltage for the OCP comparator is set by  $I \times R$  drop across the trip resistor. The  $I_{TRIP}$  current is 12.5-µA (typ) at R.T. so that the OCP point is given by following formula,

$$R_{\text{TRIP}} = \frac{R_{\text{DS(on)}} \times \left(I_{\text{OCP}} + \frac{I_{\text{RIPPLE}}}{2}\right)}{12.5 \times 10^{-6}}$$

Precaution should be taken with board layout in order to design OCP point as desired. The conversion voltage point must avoid high current path. Any voltage difference between the conversion point and VIN input for the TPS51020 is included in the threshold voltage. VIN plane layout should consider the other channels high-current path as well.

A brief discussion is required for TRIP2 function. When TRIP2 is connected, via a resistor to GND, only low-side OCP is used. This is the case for cascade configuration been selected. In this mode, UVP does not play a roll in the shut off action and there is only a short delay between the over current trigger level been hit and the power MOSFETs turn off. However, as with UVP, the SSTRTx pins are discharged and both SMPS goes though a restart.

#### LAYOUT CONSIDERATIONS

Below are some points to consider before the layout of the TPS51020 design begins.

- Signal GND and power GND should be isolated as much as possible, with a single point connection between them.

- All sensitive analog components such as INV, SSTRT, SKIP, DDR, GND, REF\_X, ENBL and PGOOD should be reference to signal GND and be as short as possible.

- The source of low-side MOSFET, the Schottky diode anode, the output capacitor and OUTGND should be referenced to power GND and be as short and wide as possible, otherwise signal GND is subject to the noise of the outputs.

- PCB trace defined as the node of LL should be as short and wide as possible.

- Connections from the drivers to the gate of the power MOSFET should be as short and wide as possible to reduce stray inductance and the noise at the LL node.

- The drain of high-side MOSFET, the input capacitor and the trip resistor should be as short and wide as possible. For noise reduction, a 22-pF capacitor C<sub>TRIP</sub> can be placed in parallel with the trip resistor.

- The output voltage sensing trace and the feedback components should be as short as possible and be isolated from the power components and traces.

- The low pass filter for VIN should be placed close to the TPS51020 and be referenced to signal GND.

- The bootstrap capacitor C<sub>BST</sub> (connected from VBST to LL) should be placed close to the TPS51020.

- VREG5 requires at least 4.7-μF bypass capacitor which should be placed close to the TPS51020 and be referenced to signal GND.

- The discharge (VO1\_VDDQ, VO2) should better have a dedicated trace to the output capacitor. In case of limiting the discharge current, series resistors should be added.

- Ideally, all of the area directly under the TPS51020 chip should also be signal GND.

Figure 4. PCB Trace Guideline

SLUS564C - JULY 2003 - REVISED OCTOBER 2008

#### **APPLICATION INFORMATION**

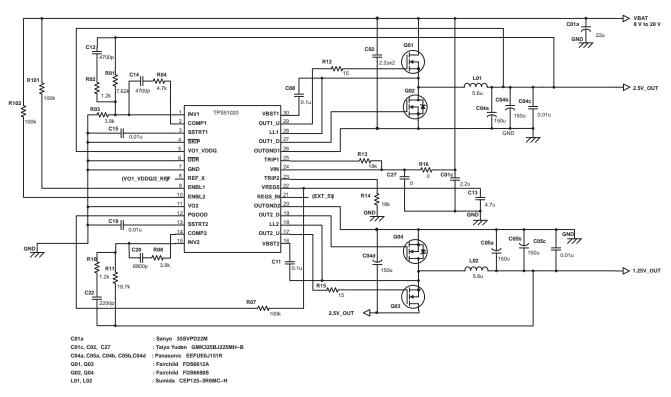

Figure 6. Typical Application Circuit: DDR(2.5V/6A + 1.25V/6A) from VBAT

### **TPS51020**

#### SLUS564C - JULY 2003 - REVISED OCTOBER 2008

#### **APPLICATION INFORMATION**

Figure 7. Typical Application Circuit: DDR (2.5V/6A + 1.25V/3A) Cascade

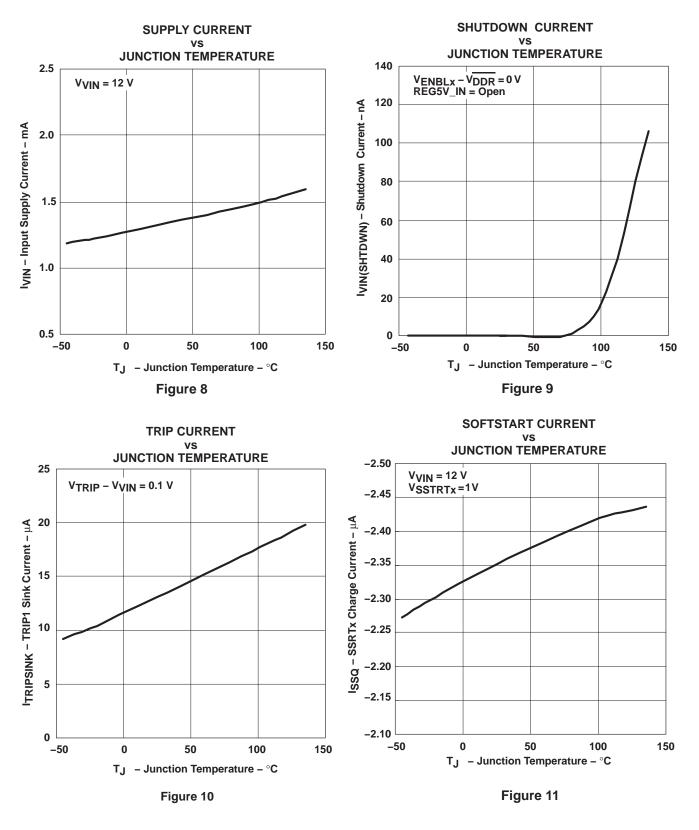

#### **TYPICAL CHARACTERISTICS**

#### **TYPICAL CHARACTERISTICS**

### **TPS51020**

SLUS564C - JULY 2003 - REVISED OCTOBER 2008

**TYPICAL CHARACTERISTICS**

## TPS51020

SLUS564C - JULY 2003 - REVISED OCTOBER 2008

24-Jan-2013

#### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package Qty | Eco Plan<br>(2)            | Lead/Ball Finish | MSL Peak Temp       | Op Temp (°C) | Top-Side Markings | Samples |

|------------------|--------|--------------|--------------------|------|-------------|----------------------------|------------------|---------------------|--------------|-------------------|---------|

| TPS51020DBT      | ACTIVE | TSSOP        | DBT                | 30   | 60          | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -40 to 85    | PS51020           | Samples |

| TPS51020DBTG4    | ACTIVE | TSSOP        | DBT                | 30   | 60          | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -40 to 85    | PS51020           | Samples |

| TPS51020DBTR     | ACTIVE | TSSOP        | DBT                | 30   | 2000        | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -40 to 85    | PS51020           | Samples |

| TPS51020DBTRG4   | ACTIVE | TSSOP        | DBT                | 30   | 2000        | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -40 to 85    | PS51020           | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND:** Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.